Clock Mux (BUFGMUX) library의 사용방법과 Timing constraints 적용방법은 ???

Clock Mux (BUFGMUX) library의 사용방법과 Timing constraints 적용방법에 대하여 설명하려고 합니다.

앞으로 설명하는 모든 자료는

UG572 (v1.7) - UltraScale Architecture Clocking Resources 와

UG974 (v2018.1) - UltraScale Architecture Libraries Guide 에 있는 내용들입니다.

(UG572, UG974 문서가 Update되었을 경우 페이지 위치가 달라질 수 있습니다. 하지만 아래 내용에 언급된 "Figure 00-00"으로 검색하시면 캡처한 그림이 위치한 페이지를 찾을 수 있습니다.)

1. BUFGMUX

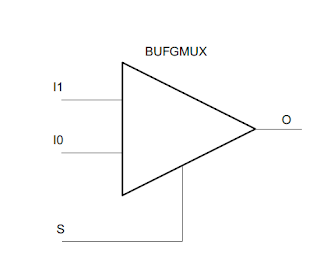

두 개의 클럭입력을 받아서 하나의 클럭만을 선택하여 사용할 경우에 아래의 그림과 같이 BUFGMUX를 사용합니다.

UG572 (v1.7) - UltraScale Architecture Clocking Resources 의 21페이지 Figure 2-9를 보면 위의 캡처화면을 확인할 수 있습니다.

위 library는 아래와 같은 timng으로 동작이 됩니다.

UG572 (v1.7) - UltraScale Architecture Clocking Resources 의 22페이지 Figure 2-10를 보면 위의 캡처화면을 확인할 수 있습니다.

위 Library를 사용할 경우에 아래의 HDL code를 사용하면 됩니다.

- VHDL의 경우는 아래와 같습니다.

BUFGMUX_inst : BUFGMUX

generic map (

CLK_SEL_TYPE => "SYNC" -- ASYNC, SYNC

)

port map (

O => O, -- 1-bit output: Clock output

I0 => I0, -- 1-bit input: Clock input (S=0)

I1 => I1, -- 1-bit input: Clock input (S=1)

S => S -- 1-bit input: Clock select

);

|

- Verilog HDL의 경우는 아래와 같습니다.

BUFGMUX #(

.CLK_SEL_TYPE("SYNC") // ASYNC, SYNC

)

BUFGMUX_inst (

.O(O), // 1-bit output: Clock output

.I0(I0), // 1-bit input: Clock input (S=0)

.I1(I1), // 1-bit input: Clock input (S=1)

.S(S) // 1-bit input: Clock select

);

|

UG974 (v2018.1) - UltraScale Architecture Libraries Guide 의 191페이지를 보면 위의 code 내용을 확인할 수 있습니다.

2. Timing Constraints for BUFGMUX

BUFGMUX를 사용할 경우의 Timing Constraints에 대하여 설명하려고 합니다.

아래의 그림을 보면 clk_a라는 input을 받아 MMCM IP를 거쳐 출력 클럭으로 mmcm_clk가 있습니다. 그리고 clk_b라는 입력 클럭이 있습니다.

BUFGMUX를 이용하여 mmcm_clk와 clk_b, 이렇게 두 클럭 중 하나를 clk_en의 control을 통해 선택하여 사용하는 디자인입니다.

위와 같이 디자인하였을 경우 아래의 timing constraints를 XDC에 적용하면 됩니다.

(아래의 XDC의 네번째 라인은 mmcm_clk을 BUFGMUX를 통하여 사용한 경우의 clkmux1과 clk_b을 BUFGMUX를 통하여 사용한 경우는 clkmux2는 서로간에 timing 관련이 없음을 정의한 부분입니다.)

(아래의 XDC의 네번째 라인은 mmcm_clk을 BUFGMUX를 통하여 사용한 경우의 clkmux1과 clk_b을 BUFGMUX를 통하여 사용한 경우는 clkmux2는 서로간에 timing 관련이 없음을 정의한 부분입니다.)

create_clock -period 5.000 -name clk_b -waveform {0.000 2.500} [get_ports {clk_b}]

create_generated_clock -source [get_pins BUFGMUX_CTRL_u0/I0] -master_clock mmcm_clk -divide_by 1 -add -name clkmux1 [get_pins BUFGMUX_CTRL_u0/O]

create_generated_clock -source [get_pins BUFGMUX_CTRL_u0/I1] -master_clock clk_b -divide_by 1 -add -name clkmux2 [get_pins BUFGMUX_CTRL_u0/O]

set_clock_groups -physically_exclusive -group clkmux1 -group clkmux2

|

아래의 첨부링크는 위 Design scheme과 Timing Constraints를 적용한 Vivado 2018.1 project file입니다.

3. Vivado Timing Report

위 2번에 첨부된 Vivado project의 Timing Report를 보면 아래와 같습니다.

위 Timing Report를 보면,

mmcm_clk을 BUFGMUX를 통하여 사용한 경우는 clkmux1에 대한 Timing Report를 보면 됩니다.

그리고, clk_b을 BUFGMUX를 통하여 사용한 경우는 clkmux2에 대한 Timing Report를 보면 됩니다.

mmcm_clk을 BUFGMUX를 통하여 사용한 경우는 clkmux1에 대한 Timing Report를 보면 됩니다.

그리고, clk_b을 BUFGMUX를 통하여 사용한 경우는 clkmux2에 대한 Timing Report를 보면 됩니다.

여러분의 FPGA 설계에 도움이 되었길 바랍니다.

그럼, 오늘도 좋은 하루 되세요.

| 이 글은 Evernote에서 작성되었습니다. Evernote는 하나의 업무 공간입니다. Evernote를 다운로드하세요. |

댓글