How to use LVDS_25 input to 3.3V HR bank

How to use

LVDS_25 input to 3.3V HR bank

Xilinx 7-Series FPGA Device는 3.3V User IO로 동작할 수 있는 HR bank가 있습니다.

LVDS_25는 Xilinx Standard IO 중 하나입니다. 그리고 LVDS_25를 사용하기 위해서는 Bank 전원이 반드시 2.5V로 인가되어야 합니다.

이는 User IO를 LVDS_25 output으로 사용할 경우에만 해당됩니다. LVDS_25 input의 경우는 Bank 전원으로 3.3V가 인가되어도 괜잖습니다.

지금부터 실제로 Vivado v2018.3에서 3.3V가 인가된 bank에 LVDS_25 input design을 구현하여 Compile이 잘 되는지 살펴보겠습니다.

1. LVDS_25 input을 3.3V Bank에 적용하여 보겠습니다.

-

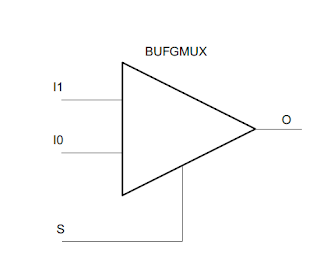

아래와 같은 schematic의 design을 예제로 사용할 것입니다.

예제에서 사용한 source code, constarints file은 test.vhd, pin_lock.xdc 입니다.

-

Synthesis, Implementation까지는 문제없이 진행됩니다. 하지만 Generate Bitstream 시에 아래와 같은 Error가 발생합니다. 하나의 Bank에 3.3V LCMOS33과 2.5V LVDS_25가 함께 사용되어 문제가 된다는 error message입니다. 그러나 LVDS_25 input의 경우는 문제가 없어야 합니다.

[DRC BIVC-1] Bank IO standard Vcc: Conflicting Vcc voltages in bank 15. For example, the following two ports in this bank have conflicting VCCOs: data_out (LVCMOS33, requiring VCCO=3.300) and clk_p (LVDS_25, requiring VCCO=2.500)

-

이러한 경우에는 test.vhd code에서 IBUFDS의 generic map 부분을 살펴보아야 합니다.

-

IBUFDS의 generic map 부분에서 "DIFF_TERM => TRUE"를 "DIFF_TERM => FALSE"로 수정하여야 합니다. 수정 후 Generate Bitstream에서 Error가 발생하지 않는 것을 확인할 수 있습니다.

-

"DIFF_TERM => FALSE"로 설정할 경우에는 아래의 그림과 같이 반드시 외부에 100오옴 termination 저항을 구현하여야 합니다.

댓글