High Speed SelectIO Wizard IP의 TX에 대한 Simulation에서 High-Z output이 나오지 않는 문제 (Vivado 2018.1)

UltraScale, UltraScale+ Device를 사용할 경우, High Speed SelectIO Wizard IP의 TX에 대한 Simulation에서 High-Z output이 나오지 않는 문제 (Vivado 2018.1)에 대하여 설명하려고 합니다.

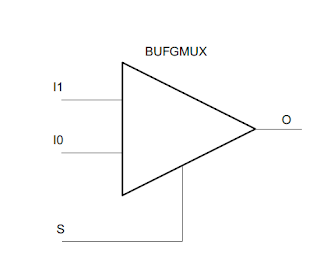

Vivado 2018.1에서 아래와 같이 High Speed SelectIO Wizard IP의 TX를 생성합니다.

IP 생성 후, Simulation을 진행합니다.

위 IP에 대한 예상되는 Simulation 결과는 다음과 같습니다.

tri_tbyte[3:0] = "0000"이면 data의 ouput은 High-Z(3-stated) 이고,

tri_tbyte[3:0] = "1111"이면 data의 ouput은 출력파형이 나옵니다.

1. High Speed SelectIO Wizard IP의 TX 생성 후, Simulation을 합니다.

High Speed SelectIO Wizard IP의 TX 생성 후, 아래와 같이 Simualtion 결과를 보면 High-Z output이 나오지 않음을 알 수 있습니다.

위 Simulation 결과에서

u1_tri_tbyte4[3:0]="0000"이지만,

u1_data1의 output이 High-Z(3-stated)가 아닌 Low로 출력되는 문제가 확인됩니다.

u1_tri_tbyte4[3:0]="0000"이지만,

u1_data1의 output이 High-Z(3-stated)가 아닌 Low로 출력되는 문제가 확인됩니다.

아래의 링크는 위 simualtion 결과를 보여주는 Vivado Project file(Vivado 2018.1)입니다.

2. Vivado 2018.1의 High Speed SelectIO Wizard IP의 bug 입니다.

이와 같은 Simualtion 결과는 Vivado 2018.1의 High Seed SelectIO Wizard IP의 tool bug로 발생된 문제입니다.

이 문제를 해결하기 위하여 patch file을 적용하여야 합니다. 아래의 링크를 클릭하면 Patch file을 download 받을 수 있습니다.

Patch 방법은 다음과 같습니다.

- 위 링크의 파일을 download 받은 후에 압축을 풉니다. ("high_speed_selectio_wiz_v3_3" 폴더를 확인할 수 있습니다.)

- 이 폴더를 C:\Xilinx\Vivado\2018.1\data\ip\xilinx 폴더에 overwrite 합니다.

- Vivado를 restart 합니다.

위 Patch 후, Simulation 결과는 다음과 같이 High-Z(3-staed)가 확인됨을 알 수 있습니다.

아래의 링크는 위 simualtion 결과를 보여주는 Vivado Project file(Vivado 2018.1)입니다.

3. 위 Bug에 대한 Vivado Update 시기는?

2018.6.18 기준으로 현재 최근 Vivado Tool Version은 2018.1입니다

위 Bug에 대한 수정은 Vivado 2018.3에서 이루어진다고 합니다. 2018년도 4분기라고 보면 됩니다. 그 때까지는 Patch file을 이용하여 이 문제를 해결하여야 합니다.

여러분의 FPGA 설계에 도움이 되었길 바랍니다.

그럼, 오늘도 좋은 하루 되세요.

| 이 글은 Evernote에서 작성되었습니다. Evernote는 하나의 업무 공간입니다. Evernote를 다운로드하세요. |

댓글